d-Matrix разработал ИИ-ускоритель Corsair, предназначенный для быстрого пакетного вывода больших языковых моделей (LLM). Ускоритель использует модифицированные ячейки SRAM для вычислений в памяти (DIMC) со скоростью около 150 терабайт в секунду. По данным EE Times, эта инновация отличается высокой производительностью и энергоэффективностью. Массовое производство Corsair планируется начать во втором квартале. Инвесторы d-Matrix включают Microsoft, Nautilus Venture Partners, Entrada Ventures и SK hynix.

d-Matrix специализируется на пакетном инференсе с низкой задержкой. Сервер d-Matrix с Llama3-8B (16 ускорителей в четырёхчиплетных картах, составляющих восемь модулей) способен обрабатывать 60 тысяч токенов в секунду с задержкой в 1 миллисекунду на токен. Стойка d-Matrix с Llama3-70B (128 чипов) обеспечивает генерацию 30 тысяч токенов в секунду с задержкой в 2 миллисекунды на токен. Клиенты d-Matrix могут ожидать достижения этих показателей при размерах пакетов порядка 48–64 (в зависимости от длины контекста), как сообщила Sree Ganesan, руководитель отдела продуктов d-Matrix, изданию EE Times.

Производительность оптимизирована для обработки моделей с числом параметров до 100 миллиардов на одном сервере. Это реалистичный сценарий использования LLM, по мнению Ганесан. В таких условиях решение d-Matrix обеспечивает десятикратное преимущество в интерактивности (время до получения токена) по сравнению с традиционными ускорителями, такими как NVIDIA H100. Corsair предназначен для моделей с меньшим количеством параметров (менее 70 миллиардов), подходящих для генерации кода, создания видео или искусственного интеллекта агентов, требующих высокой интерактивности в сочетании с пропускной способностью, энергоэффективностью и низкой стоимостью.

Ранние версии архитектуры d-Matrix включали блоки MAC на основе ячеек SRAM с дополнительными транзисторами для операций умножения. Сложение осуществлялось аналоговым способом с использованием разрядных линий, измерения тока и аналого-цифрового преобразования. В 2020 году компания представила чиплетную платформу Nighthawk на основе этой архитектуры. «Nighthawk показал, что мы можем значительно улучшить точность по сравнению с традиционными аналоговыми решениями, но мы всё ещё отстаём на несколько процентных пунктов от традиционных решений, таких как GPU», — сообщил генеральный директор d-Matrix Сид Шет в интервью EE Times.

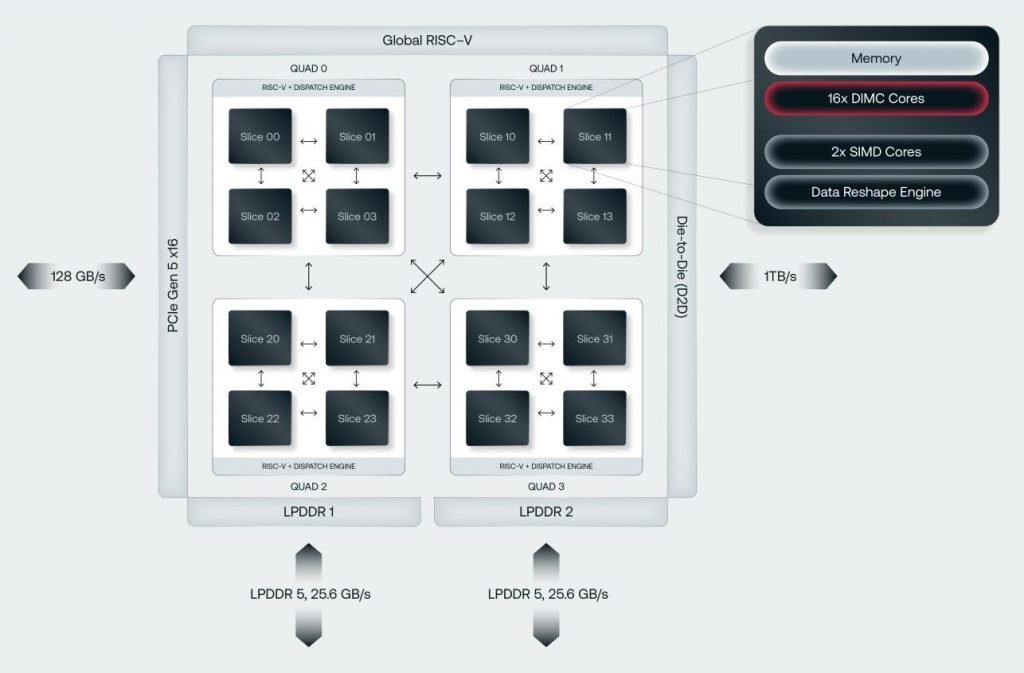

И всё же потенциальные клиенты выразили обеспокоенность возможным снижением точности при использовании такого подхода, поэтому компания была вынуждена сделать выбор в пользу полностью цифрового сумматора. ASIC d-Matrix состоит из четырёх чипсетов, каждый из которых содержит четыре вычислительных блока, соединённых через DMX Link по схеме «каждый с каждым», а также планировщик и ядро RISC-V. В каждом вычислительном блоке есть 16 ядер DIMC, состоящих из наборов SRAM-ячеек (64 × 64), а также два SIMD-ядра и преобразователь данных. В общей сложности доступно 1 ГБ SRAM с пропускной способностью 150 ТБ/с.

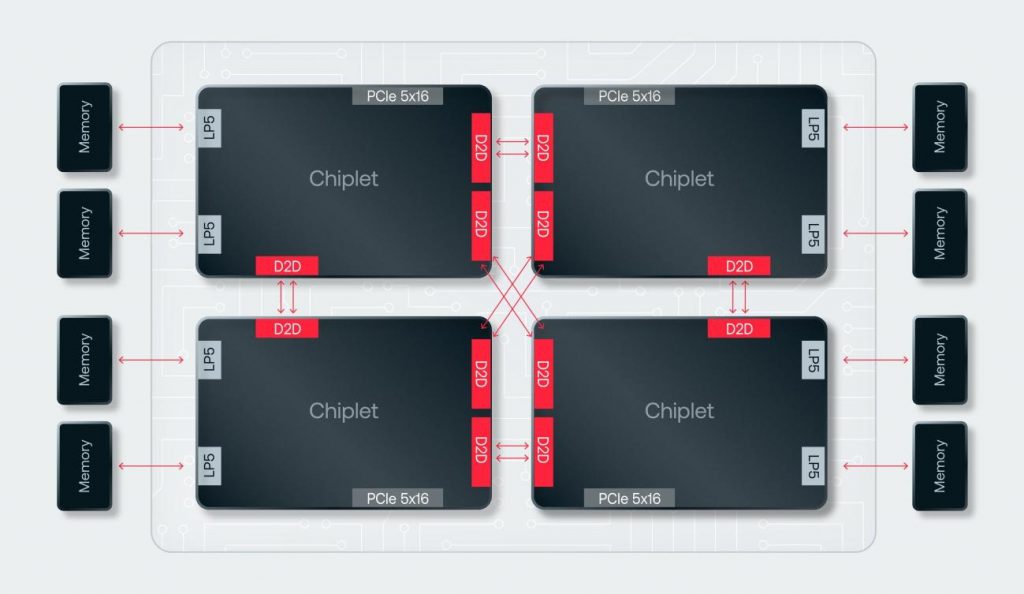

ASIC интегрирован с 128 ГБ LPDDR5 (до 400 ГБ/с) через органическую подложку (без использования дорогого кремниевого интерпозера). Хотя текущее поколение ASIC содержит только четыре чиплета из-за ограничений подложки, в будущем их количество будет увеличено. Внешние интерфейсы ASIC включают стандартный PCIe 5.0 x16 (128 ГБ/с) и фирменный интерфейс DMX Link (1 ТБ/с) для соединения чипсетов.

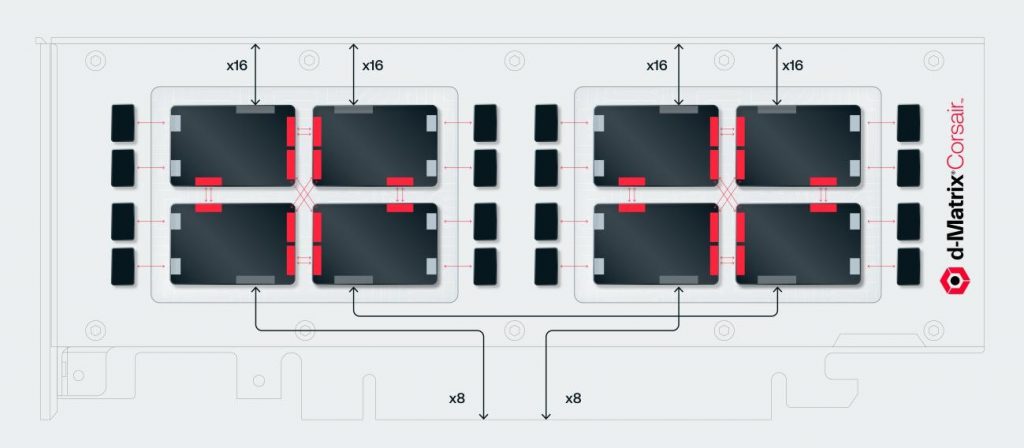

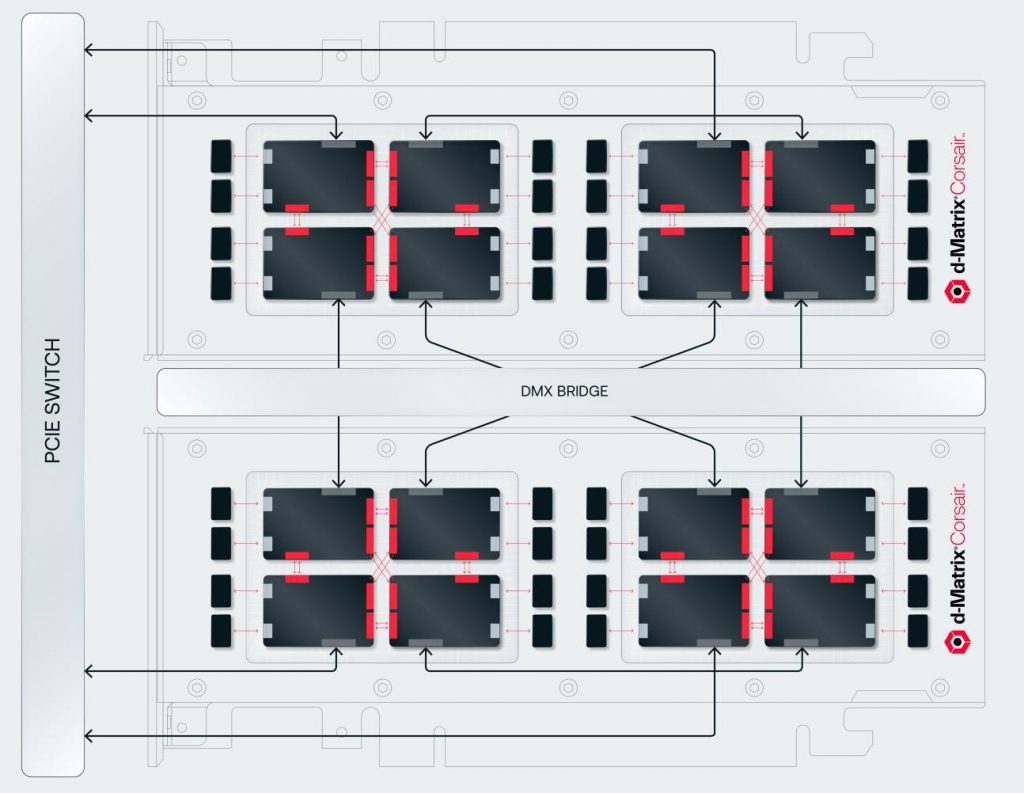

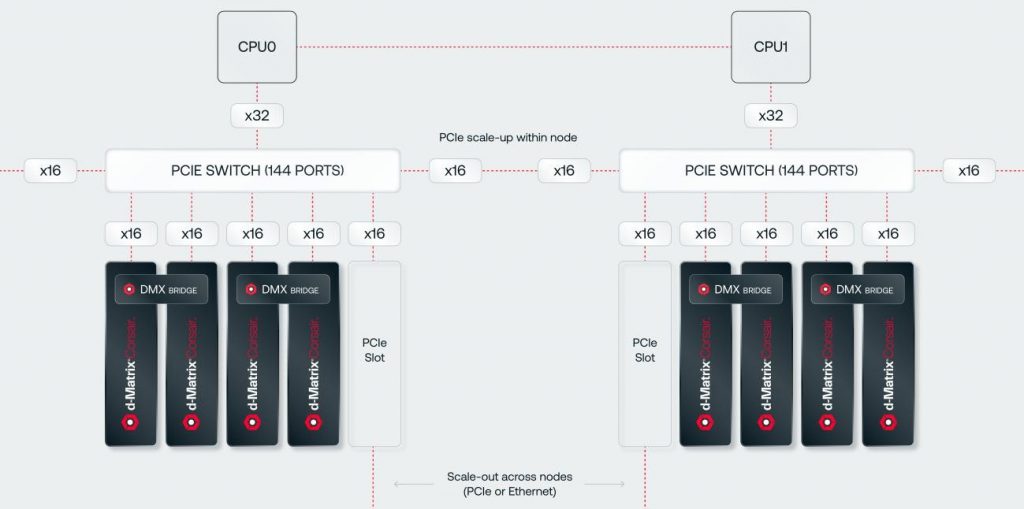

Карта FHFL от Corsair оснащена двумя ASIC d-Matrix (всего восемь чиплетов) и имеет TDP 600 Вт. Этот ускоритель поддерживает форматы данных OCP MX и обеспечивает производительность до 2400 терафлопс в вычислениях MXINT8 или 9600 терафлопс в MXINT4. Две карты Corsair могут быть соединены с помощью моста DMX Bridge с пропускной способностью 512 гигабайт в секунду. Этого достаточно для использования тензорного параллелизма, согласно заявлению производителя. Дополнительное масштабирование возможно благодаря использованию PCIe-коммутации, поэтому d-Matrix совместим с GigaIO и Liqid. В одно шасси можно установить восемь карт Corsair, а в стойку, потребляющую около 6–7 киловатт, — 64 карты.

D-Matrix уже разрабатывает следующее поколение ASIC под названием Raptor, которое ожидается в 2026 году. Raptor будет ориентирован на «умные» модели и получит больше памяти благодаря размещению DRAM прямо на вычислительных чиплетах. SRAM-чиплеты Raptor также перейдут с 6-нанометрового техпроцесса TSMC, используемого при производстве Corsair, на 4 нанометра без значительных изменений микроархитектуры. Компания утверждает, что потратила два года на сотрудничество с TSMC для создания 3D-упаковки для нового поколения ASIC.

Согласно информации от EETimes, команда разработчиков программного обеспечения d-Matrix вдвое превышает команду разработчиков аппаратных средств (120 против 60). Стратегия компании в сфере программного обеспечения заключается в активном использовании открытой экосистемы, включая PyTorch, OpenAI Triton, MLIR и OpenBMC. Все вместе они формируют программный стек Aviator, который занимается преобразованием моделей в цифровые форматы d-Matrix, применяет фирменные методы сжатия, компилирует их, распределяет нагрузку между картами и серверами, а также контролирует выполнение моделей, включая обработку множества запросов.

По материалам:

servernews