Renesas Electronics, один из ведущих производителей электроники, объявил о создании своего собственного 32-разрядного процессорного ядра, основанного на открытой архитектуре набора инструкций RISC-V (RISC-V Instruction Set Architecture, или ISA). Это дополнение к существующему семейству 32-разрядных микроконтроллеров Renesas, которое включает проприетарные продукты на базе Arm Cortex-M архитектуры.

RISC-V-ядро Renesas может быть использовано для создания процессоров общего назначения, которые могут найти применение в различных областях. Устройства Интернета вещей, потребительская электроника, медицинское оборудование, индустриальные системы – все это возможные сферы применения процессоров на базе RISC-V-ядра Renesas.

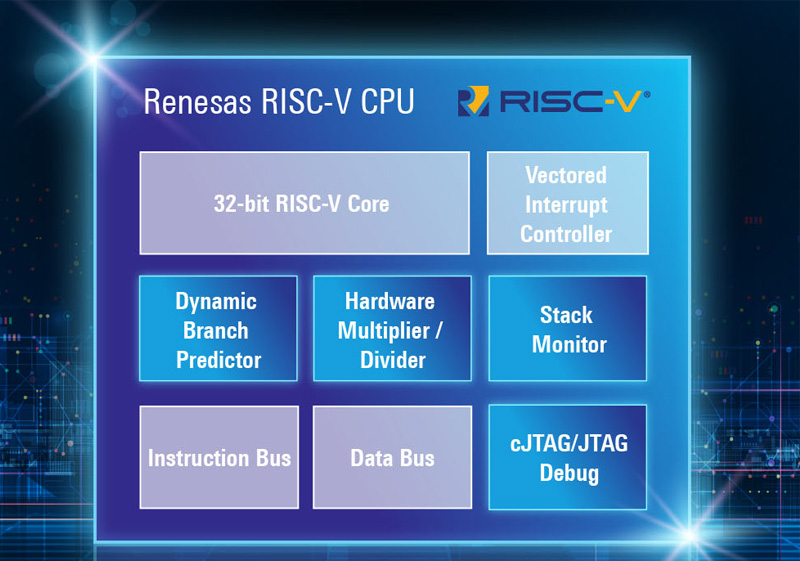

Ядро может использоваться как основной контроллер приложений или дополнительный узел в SoC (системе на кристалле). Оно также подходит для использования во внутрикристальных подсистемах и специализированных изделиях. Производительность ядра оценивается в 3,27 CoreMark/МГц, что превосходит показатели других решений в своем классе.

В RISC-V ядре Renesas реализованы расширения ISA, включая M (целочисленное умножение/деление), A (атомарные операции с памятью), C (сжатый формат команд, подмножество RV32I) и B (инструкции для манипуляций с битами). Компания планирует выпустить свой первый микроконтроллер на базе RISC-V и инструменты разработки в первом квартале 2024 года, а также раскрыть технические детали продукта.

Источник servernews