Потребность в более скоростных интерфейсах существовала в мире ИТ всегда, но за последние годы она обострилась: третья версия PCI Express пробыла с нами почти десятилетие, и лишь сейчас, проводив 2020 год, можно сказать о сколько-нибудь заметном распространении PCI Express 4.0.

Урок усвоен и с PCIe 5.0 аналогичной истории не повторится: практически все разработчики процессоров и прочих компонентов изначально закладывают поддержку пятой версии в свои новые решения. Среди лидеров в этой области — компания PLDA, продемонстрировавшая работоспособность своих компонентов PCI Express 5.0 и CXL.

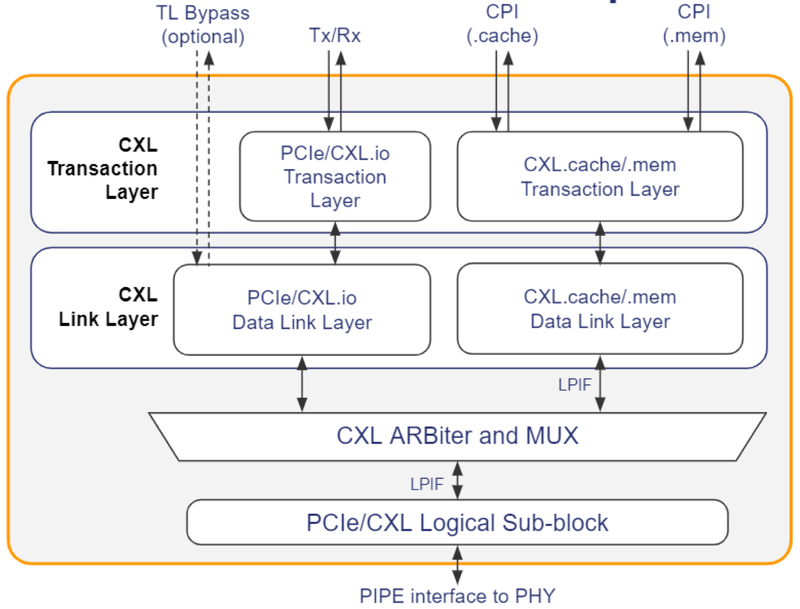

Говоря о CXL, мы неизбежно подразумеваем PCIe 5.0 — именно PCI Express пятой версии является физической основой нового протокола скоростных межсоединений Compute Express Link. CXL дополняет PCIe 5.0 рядом интересных и востребованных в мире HPC возможностей, но речь сейчас не об этом, а о том, что родственность стандартов упрощает разработку IP-блоков с их поддержкой.

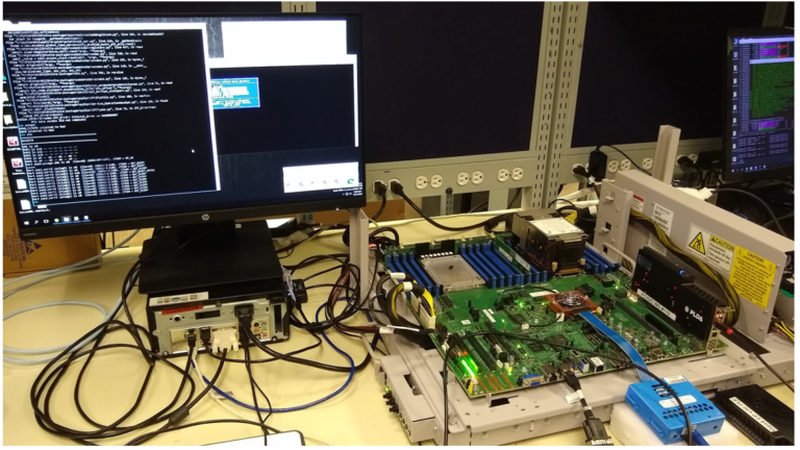

Компания PLDA является активным разработчиком IP-модулей, причём, специализируется она именно на высокоскоростных интерфейсах, участвуя в разработке стандарта PCI Express c 2001 года. Стандарты, сколь угодно совершенные в теории, мертвы без реального работоспособного «кремния», и здесь PLDA оказалась в числе лидеров, успешно продемонстрировав работу своего контроллера PCI Express 5.0 и доказав работоспособность CXL в системах на базе инженерных образцов Intel Sapphire Rapids.

Следует отметить, что контроллер PLDA XpressRICH не монолитен, за физическую часть (PHY) в демонстрационной системе отвечал блок, разработанный Broadcom. Несмотря на это, IP-модули продемонстрировали слаженную работу и целостность сигнала в различных тестовых сценариях. PLDA утверждает, что данную связку разработчики новых SoC могут использовать смело — качество работы гарантируется.

Две тестовые платы успешно устанавливали стабильную связь на скорости 32 ГТ/с, для тестирования были использованы компоненты Xilinx Vivado ILA и анализатор PCIe Viavi. Также контроллер PLDA без проблем работал в режиме совместимости с предыдущими версиями PCIe на скоростях 16, 8, 5 и 2,5 ГТ/с.

Демонстрация CXL использовала другой набор компонентов. В этом сценарии разработка PLDA под названием XpressLINK была воплощена в ПЛИС на PCIe-платах. Новый контроллер поддерживает все основные суб-протоколы CXL, описанные в версии 2.0: CXL.io, CXL.cache и CXL.mem. Платформой здесь послужили системы, оснащённые прототипами процессоров Intel Xeon Sapphire Rapids.

Демонстрация, проведённая в рамках давнего сотрудничества PLDA и подразделения Intel Industry Enabling Labs, показала полную работоспособность новинок, а также доказала, что контроллер CXL обеспечивает самую низкую латентность в своём классе. Последнее крайне важно, поскольку CXL пророчат в качестве основы для суперкомпьютеров и кластерных систем нового поколения.

Контроллер PLDA XpressLINK может быть реализован в качестве строительного блока для SoC, как отдельный ASIC-чип, а также в виде ПЛИС. Он доступен для лицензирования, чем уже воспользовались некоторые крупные разработчики микроэлектроники.