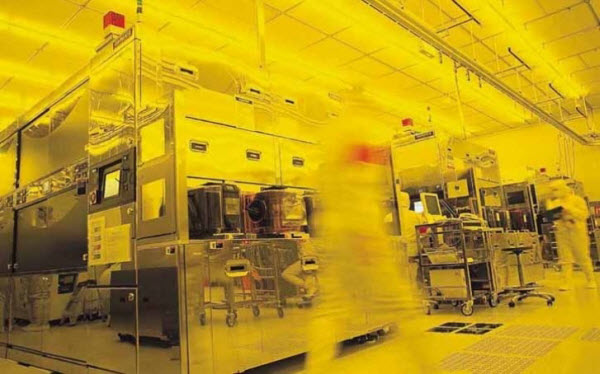

Тайваньская TSMC, занимающаяся разработкой и производством полупроводниковых изделий, провела ежегодную конференцию Technology Symposium, на которой была анонсирована дорожная карта компании на последующие два года. Сообщается, что уже сегодня TSMC запустила первый этап подготовительных работ по созданию 2-нм технологического производства и даже сделала первые шаги к началу строительству завода и исследовательского центра. Для этого TSMC приобрела землю в Синьчжу, где планируется построить новый центр по исследованиям и разработкам TSMC.

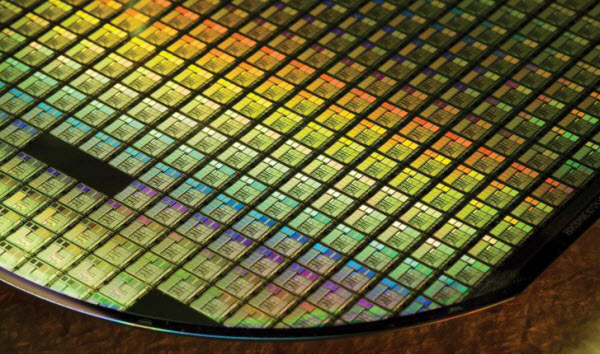

В настоящее время компания TSMC производит чипсеты по 5-нм техпроцессу (кодовое название N5). Ожидается, что основным клиентом TSMC на ближайшие время останется американская Apple, а основным изделием, для которого будут выпускаться эти чипы, будет iPhone 12.

Рассказывая о планах по развитию 3 нм техпроцесса (кодовое наименование N3), тайваньский производитель сообщил, что для этого планируется применять иное «архитектурное решение», чем то, которое выбрал Samsung, главный конкурент TSMC. Массовый выпуск процессоров на базе этого техпроцесса должен начаться во втором полугодии 2022 года.

Между этапами N5 и N3 запланировано несколько промежуточных стадий. Первым из них станет этап N5P. Он будет связан с созданием оптимизированного 5 нм технологического процесса, который позволит поднять производительность выпускаемых проводниковых изделий на 5% при снижении их энергозатрат на 10%. Переход на этот промежуточный техпроцесс и вывод на стадию массового производства намечен на 2021 год.

Следом запланирован второй промежуточный этап — N4. Он будет представлять собой дальнейшее развитие отдельных технологических процессов в рамках общего процесса фотолитографии в глубоком ультрафиолете (EUV). Разработка будет вестись вплоть до IV квартала 2021 года, переход к массовому производству намечен на начало 2022 года.

В отличие от подхода, выбранного Samsung и его подразделением GAA, TSMC планирует выпускать 3-нм чипсеты, выстроенные на транзисторах, которые будут изготавливаться по техпроцессу FinFET. По имеющимся сведениям, TSMC планирует использовать для решения N3 ряд «инновационных функций». Согласно предварительным оценкам, это позволит повысить их производительность на 10-15%, одновременно снизив энергопотребление на 30%. Габаритные размеры новых чипов N3 снизятся в 1,7 раза, то есть размеры 3-нм чипа будут составлять лишь 0,58 часть от размеров 5 нм чипа.

Впрочем, миниатюризация распространится не на все элементы конструкции чипа, отмечают в TSMC. Отдельные элементы будут отличаться по степени миниатюризации по сравнению с предыдущими образцами, обеспечивая при этом наилучшую производительность. Из-за ограничений на развитие статической памяти с произвольным доступом (SRAM, static random access memory) кристалл N3 будет фактически примерно на 26% меньше, чем N5.

Выход чипов N3 на массовый рынок намечен на конец 2022 года.

Технологический процесс производства полупроводников на базе 2-нм норм будет разрабатываться по технологии GAA (gate-all-around), а не FinFET, который был выбран для 3-нм производства.