Тайваньская компания TSMC, занимающаяся разработкой и производством полупроводниковых изделий, провела официальный анонс, где рассказала о достижениях в области разработки нового 3-нм технологического процесса для производства полупроводников.

Согласно объявленным данным, созданный в TSMC техпроцесс полупроводникового производства по нормам 3 нм обеспечивает достижение рекордного уровня плотности размещения проводников на поверхности — 250 млн транзисторов / мм².

Для справки: процессор Kirin 990 5G, выпускаемой компанией TSMC по 7-нм техпроцессу с применением новейшей технологии фотолитографии в глубоком ультрафиолете (EUV), имеет размер 113,31 мм² и плотность транзисторов 10,3 млрд. шт. Это означает, что в среднем плотность размещения транзисторов составляет 90 млн. шт./ мм².

Исходя из этого сравнения, можно заявить, что достигнутая плотность размещения для технологического 3-нм образца в 3,6 раза больше, чем достигаемая при использовании 7-нм техпроцесса.

Но главный вопрос, который интересует сейчас: Насколько может вырасти производительность при переходе на новую плотность размещения транзисторов?

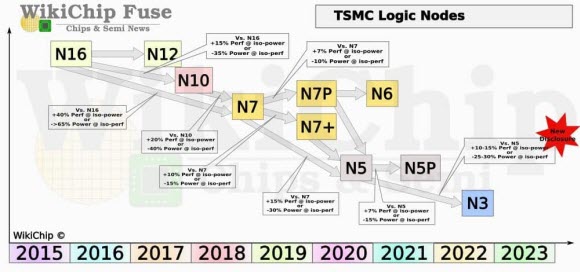

По данным TSMC, прежний переход технологии полупроводниковой литографии с 7 нм на 5 нм уровень позволил поднять производительность на 10-15%, а энергопотребление снизить на 25-30%. Нынешний переход с норм 5 нм на 3 нм позволяет рассчитывать, что производительность может вырасти на 5%, а потребление энергии также возрастет на 15%.

Оценка физической плотности размещения транзисторов показывает по данным TSMC, что прирост при замене техпроцесса с 5-нм на 3 нм составит 1,7 раза.

Теоретически уровень достижимой физической плотности 3 нм процесса, согласно WikiChip, может достигать почти 300 млн транзисторов / мм². Нынешний результат, показанный TSMC на уровне 250 млн транзисторов / мм², указывает, что еще не все резервы исчерпаны.

Пробное производство кремневых пластин 3-нм начнется, по словам СиСи Вей (CC Wei), генерального директора TSMC, в 2021 году. Их запуск в массового производства намечен на вторую половину 2022 года.

Если же говорить о реализации технологии, то в TSMC уже оценили существующие варианты производства и отдали предпочтение сохранить нынешний способ — FinFET. По мнению TSMC, это обеспечит наилучшие показатели по затратам и энергоэффективности.

Главный конкурент TSMC, компания Samsung, сделал другой выбор. Samsung делает ставку на смену технологии при переходе на 3 нм нормы. Она собирается отказаться от FinFET и использовать новую технологию кольцевого затвора GAA (Gate All Around). Эта технология относится к следующему этапу эволюции. Она позволяет повысить производительность, но их производство станет более сложным и более дорогим. Поэтому переход на новый уровень может затянуться.